## Diameter dependent transport properties of gallium nitride nanowire field effect transistors

Abhishek Motayed,<sup>a)</sup> Mark Vaudin, and Albert V. Davydov

National Institute of Standards and Technology, Gaithersburg, Maryland 20899

John Melngailis

Department of Electrical and Computer Engineering, University of Maryland, College Park, Maryland 20742

Maogi He and S. N. Mohammad

Department of Electrical and Computer Engineering, Howard University, Washington, District of Columbia 20059

(Received 18 September 2006; accepted 9 December 2006; published online 22 January 2007)

The authors report transport property measurements of individual GaN nanowire field effect transistors and the correlation of the electron mobilities with the existence of grain boundaries in these nanowires. Room temperature field effect electron mobilities as high as  $319 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  were obtained for the 200 nm diameter nanowires. Mobilities calculated from these reliable nanowire field effect transistors indicated that the surface scattering plays a dominant role in smaller diameter nanowires, whereas for intermediate diameter devices transport is dominated by grain boundary scattering. Reduction of the mobility with decreasing diameter of nanowires can be explained using "continuous surface" model. © 2007 American Institute of Physics. [DOI: 10.1063/1.2434153]

Nanowires of gallium nitride and other related nitrides with direct band gaps, large breakdown fields, and high saturation velocities are the ideal candidates for efficient nanoscale ultraviolet/visible light emitters, detectors, and radiation hard, high temperature nanoelectronic devices. In the last few years, there has been significant progress in GaN nanowire growth, <sup>1–3</sup> characterization,<sup>4</sup> and individual device fabrication<sup>5–11</sup> though there are very few reports<sup>7,9,10</sup> of detailed transport property measurements in these nanostructures. Correlating the transport properties of these nanowire devices with their structural characteristics is essential for understanding (a) the effects of growth parameters on the device properties and (b) the conduction processes in these nanostructures.

In this letter, we report the results of detailed electrical measurements of GaN nanowire field effect transistor (NWFET) devices, assembled on  $SiO_2$  (600 nm) coated Si substrates utilizing dielectrophoretic forces. The electron backscattered diffraction (EBSD) was used to study the effect of grain boundaries on the transport properties of these nanowires. Diameter dependent electron mobility measurements revealed that larger diameter nanowires exhibited significantly higher mobility than nanowires with smaller diameters. A scattering model, taking into account the surface effects, can explain the observed dependence of mobility on the nanowire diameter.

Nanowires with diameters ranging from 50 to 300 nm and lengths up to 200  $\mu$ m were grown by direct reaction of metal gallium vapor with flowing ammonia at 850–900 °C in a horizontal furnace.<sup>2</sup> EBSD confirmed that the growth direction of the nanowires was along the *a* axis of the wurtzite structure.<sup>11</sup> A suspension of nanowires in isopropanol, formed by sonication, was dispersed on a 600 nm (thermally grown) SiO<sub>2</sub> coated Si substrate with Ti/Al/Ti

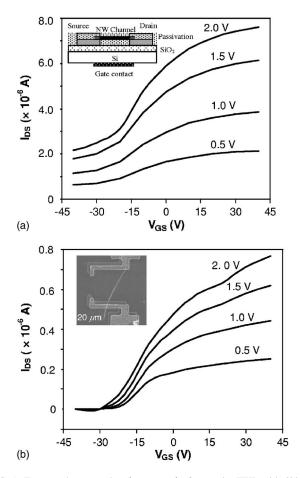

(30/100/30 nm) metal pads. Alignment of the nanowires were obtained by applying 20 V peak-to-peak ac voltage at 1 kHz between the metal pads,<sup>12</sup> followed by deposition of a 50 nm SiO<sub>2</sub> passivation layer using plasma enhanced chemical vapor deposition. The oxide was removed over metal-nanowire contact area and a second metal layer (Ti/Al/Ti/Au) (30/100/30/30 nm) was deposited [schematic of NWFET is shown in the inset of Fig. 1(a) and field emission scanning electron microscope (FESEM) image of a complete device is shown in the inset of Fig. 1(b)]. The source drain current  $(I_{DS})$  was measured using a subfemtoampere source measure unit. After the completion of electrical measurements, FESEM was used to study the morphology of the nanowire devices and measure the diameters of the nanowires. EBSD was carried out using the same FESEM at voltages of 15 and 20 keV using an emission current of 20 nA. Software was used to analyze the Kikuchi diffraction patterns and predict the crystal orientation of the nanowires.

Nanowire channel current modulation has been achieved by applying bias to the Si substrate with Al back contacts. Depletion mode behavior with *n*-type conductivity is observed in all devices, possibly due to the presence of lattice defects and impurities such as oxygen. The majority of the NWFETs could not be fully depleted, even at -40 V gate bias, which is often observed with back gated NWFETs,<sup>6-8</sup> due to the poor gate modulation in this geometry. It is possible to completely deplete the channel by using a thinner gate oxide. These devices had high drain-source current  $(I_{DS})$ in the range of  $10^{-6}-10^{-5}$  A for 1 V drain-source voltage  $(V_{\rm DS})$  at 0 V gate-source voltage  $(V_{\rm GS})$  with linear  $I_{\rm D}$  vs  $V_{\rm DS}$ characteristics demonstrating Ohmic characteristics of the source drain contacts.<sup>12</sup> Figure 1(a) shows the plot of  $I_{DS}$  vs  $V_{\rm GS}$  of a nanowire device (diameter of 192 nm, length of 44  $\mu$ m) with different V<sub>DS</sub>. Channel current saturation was not observed in these nanowires even at high values of  $V_{DS}$

90, 043104-1

<sup>&</sup>lt;sup>a)</sup>Electronic mail: amotayed@nist.gov

<sup>© 2007</sup> American Institute of Physics

Downloaded 23 Jan 2007 to 129.6.196.30. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 1. Transconductance plots ( $I_{\rm DS}$  vs  $V_{\rm GS}$ ) of nanowire FETs with 600 nm gate oxide for different  $V_{\rm DS}$  for (a) nanowire with diameter of 195 nm and length of 44  $\mu$ m with the schematics shown in the inset and (b) nanowire with diameter of 95 nm and length of 35  $\mu$ m with SEM scan of finished device shown in inset. Value of  $V_{\rm DS}$  is shown over each plot.

(±4 V). The electron field effect mobility ( $\mu$ ) is calculated using the relationship<sup>8</sup>

$$\mu = \frac{g_m}{V_{\rm DS}} \frac{L \ln(4t_{\rm ox}/d)}{2\pi\varepsilon_0 \varepsilon_{\rm SiO_2}},\tag{1}$$

where transconductance  $(g_m)$  is the slope  $\partial I_{DS}/\partial V_{GS}$  of the  $I_{DS}$  vs  $V_{GS}$  plot measured at  $V_{GS}=0$  V and  $V_{DS}=1$  V, L and d are the length and diameter of the nanowire, respectively,  $t_{ox}$  is the oxide thickness (600 nnm),  $\varepsilon_0$  is the permittivity of free space, and  $\varepsilon_{SiO_2}$  is the permittivity of silicon dioxide. The calculated mobility for this particular device was 230 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. A mobility of 319 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> was calculated for a device with 200 nm diameter nanowire and 56  $\mu$ m length, which is significantly higher than the majority of the GaN NWFET results published so far,<sup>6–8</sup> except for the report of mobility in excess of 600 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for GaN nanowire FET by Huang *et al.*<sup>5</sup>

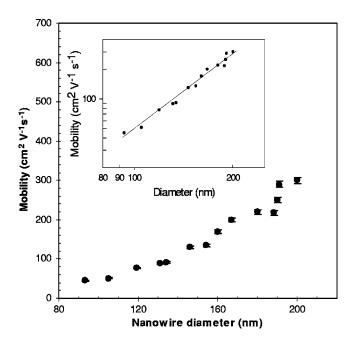

Complete channel depletion at gate voltage of -40 to -30 V with on-off current ratio of  $10^7$  is only observed in nanowires of diameter of 100 nm and less. Figure 1(b) shows the  $I_{\rm DS}$  vs  $V_{\rm GS}$  plot of a nanowire device (diameter of 95 nm, length of 35  $\mu$ m) with  $V_{\rm DS}$  varied from 0.5 to 2 V. The electron mobility of this device was 40 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Mobility measurement on NWFETs with different diameters revealed that mobility in these devices increase with the diameter of the nanowire (Fig. 2). Mobility for 95 nm diameter nanowire was 40 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, whereas mobility of a 200 nm diameter

FIG. 2. Plot of GaN nanowire FET room temperature mobility vs nanowire diameter. The inset is logarithmic plot of same curve with slope of 1.3.

nanowire was as high as  $319 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . For the devices that could be completely turned off, carrier concentrations calculated using threshold voltage and calculated capacitances<sup>5</sup> were in the range of  $2 \times 10^{18}$  cm<sup>-3</sup>. Assuming that the background carrier concentration is invariant from one device to another, FET mobility values for 200 nm diameter nanowires are similar to the electron Hall mobility values in GaN epitaxial thin films of equivalent carrier concentrations.<sup>13</sup> Lower mobility in smaller diameter nanowires could be explained by enhanced surface scattering. The effect of sidewall scattering in the overall mobility in these nanowires can be modeled using a simple "continuous surface model."<sup>14</sup> In this model, increased scattering at the surface is accounted for by a surface layer of width w, in which the relaxation time is considerably smaller than that in the interior of the wire. Assuming that surface depletion and surface defects give rise to this surface layer, the width of this layer should remain constant for different wires with the same carrier concentration. The ratio of inner volume to the surface layer volume of a nanowire will be greater in larger diameter nanowires than their smaller diameter counterparts. Hence effective mobilities calculated by averaging the geometric distribution of the relaxation time weighted by the relative carrier concentration will be larger in wider nanowires.

The electron mobility of nanowires as a function of diameter is shown in the inset of Fig. 2 plotted on logarithmic axes. Use of a  $\mu \propto d^p$  relationship yields a least squares fit with p=1.3. An attempt is underway to understand the physical origin of this relationship. In order to be physically realistic, the plot should asymptotically approach the bulk GaN mobility for larger diameters, with a negative curvature. It is a possibility that additional factors are reducing the mobilities of intermediate diameter nanowires (120 nm  $\leq d$  $\leq 160$  nm). In order to investigate such a possibility, after electrical measurements the oxide was completely etched and EBSD was used to study the microstructural properties of all the nanowires devices. It was observed that some of the low mobility nanowires with diameters above 120 nm were

Downloaded 23 Jan 2007 to 129.6.196.30. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

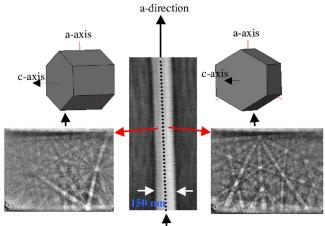

Grain boundary

FIG. 3. (Color online) EBSD patterns from two different points on the surface of a 150 nm diameter nanowire. From these patterns, the crystal orientations of the two halves of the bicrystal were determined, as illustrated by the crystal schematics. The *a* axis of each crystal is parallel to the growth direction (as expected) but there is a  $42^{\circ}$  rotation between the *c* directions about the common *a* axis. The dotted line on the nanowire indicates the grain boundary as inferred from the patterns.

bicrystals with grain boundaries running parallel along the length of the wire. Figure 3 shows the Kikuchi diffraction patterns and the crystal orientations from two different points of a 150 nm diameter nanowire FET device (mobility of 120 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) using EBSD technique. The diffraction patterns did not change when the electron beam was moved along the length of the wire, whereas the diffraction patterns from two different points along the diameter corresponding to the left and right sides of the wire clearly indicated the presence of bicrystals with their *a* axes parallel to the growth direction (as expected) but with a 42° angle of rotation between the *c* directions about the common *a* axis. Higher mobility nanowires studied using EBSD did not reveal the presence of grain boundaries. Grain boundaries were also absent from smaller diameter nanowires.

In summary, transport measurements were performed on individual GaN nanowire transistors having a range of diameters exhibited pronounced size effect in the measured field effect mobility. Room temperature mobility from 40 to 319 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> was measured for nanowires from 95 to 200 nm diameter, respectively. Lower mobility in thinner nanowires (diameter less than 100 nm) can be explained by enhanced surface scattering, whereas EBSD showed that the grain boundary scattering might reduce the mobilities in the intermediate diameter nanowire (diameter between 120 and 180 nm). Further studies are needed to isolate and quantify the effects of surface, grain boundary, defect, and bulk scattering mechanisms on the overall mobility in these nanowire FETs.

- <sup>1</sup>H. Y. Peng, X. T. Zhou, N. Wang, Y. F. Zheng, L. S. Liao, W. S. Shi, C. S. Lee, and S. T. Lee, Chem. Phys. Lett. **327**, 263 (2000).

- <sup>2</sup>Maoqi He, Indira Minus, Piezhen Zhou, S. Noor Mohammed, Joshua B. Halpern, Randy Jacobs, Wendy L. Sarney, Lourdes Salamanca-Riba, and R. D. Vispute, Appl. Phys. Lett. **77**, 3731 (2000).

- <sup>3</sup>G. S. Cheng, L. D. Zhang, Y. Zhu, G. T. Fei, L. Li, C. M. Mo, and Y. Q. Mao, Appl. Phys. Lett. **75**, 2455 (1999).

- <sup>4</sup>T. Kuykendall, P. J. Pauzauskie, Y. Zhang, J. Goldgerger, D. Sirbuly, J. Denlinger, and P. Yang, Nat. Mater. **3**, 524 (2004).

- <sup>5</sup>Y. Huang, X. Duan, Y. Cui, and C. M. Lieber, Nano Lett. 2, 101 (2002).

<sup>6</sup>J.-R. Kim, H. M. So, J. W. Park, J.-J. Kim, J. Kim, C. J. Lee, and S. C. Lyu, Appl. Phys. Lett. 80, 3548 (2002).

- <sup>7</sup>E. Stern, G. Cheng, E. Cimpoiasu, R. Klie, S. Guthrie, J. Klemic, I. Kretzschmar, E. Steinlauf, D. T.-Evans, E. Broomfield, J. Hyland, R. Koudelka, T. Boone, M. Young, A. Sanders, R. Munden, T. Lee, D. Routenberg, and M. A. Reed, Nanotechnology **16**, 2941 (2005).

- <sup>8</sup>H.-Y. Cha, H. Wu, M. Chandrashekhar, Y. C. Choi, S. Chae, G. Koley, and M. G. Spencer, Nanotechnology **17**, 1264 (2006).

- <sup>9</sup>J.-R. Kim, B.-K. Kim, I. J. Lee, J.-J. Kim, J. Kim, S. C. Lyu, and C. J. Lee, Phys. Rev. B **69**, 233303 (2004).

- <sup>10</sup>C. Y. Nam, D. Tham, and J. E. Fischer, Nano Lett. **5**, 2029 (2005).

- <sup>11</sup>Abhishek Motayed, Albert V. Davydov, Mark D. Vaudin, Igor Levin, John Melngailis, and S. N. Mohammad, J. Appl. Phys. **100**, 024306 (2006).

- <sup>12</sup>Abhishek Motayed, Maoqi He, Albert V. Davydov, John Melngailis, and S. N. Mohammad, J. Appl. Phys. **100**, 114310 (2006).

- <sup>13</sup>W. Gotz, N. M. Johnson, C. Chen, H. Liu, C. Kuo, and W. Imler, Appl. Phys. Lett. **68**, 3144 (1996).

- <sup>14</sup>V. S. Sundaram and A. Mizel, J. Phys.: Condens. Matter 16, 4697 (2004).