Nanotechnology **25** (2014) 155702 (7pp)

doi:10.1088/0957-4484/25/15/155702

# Electrical transport and low-frequency noise in chemical vapor deposited single-layer MoS<sub>2</sub> devices

Deepak Sharma<sup>1,2</sup>, Matin Amani<sup>3</sup>, Abhishek Motayed<sup>2,4</sup>, Pankaj B Shah<sup>3</sup>, A Glen Birdwell<sup>3</sup>, Sina Najmaei<sup>5</sup>, Pulickel M Ajayan<sup>5</sup>, Jun Lou<sup>5</sup>, Madan Dubey<sup>3</sup>, Qiliang Li<sup>1</sup> and Albert V Davydov<sup>2</sup>

E-mail: amotayed@nist.gov and amotayed@umd.edu

Received 6 January 2014 Accepted for publication 13 February 2014 Published 18 March 2014

### **Abstract**

We have studied temperature-dependent (77–300 K) electrical characteristics and low-frequency noise (LFN) in chemical vapor deposited (CVD) single-layer molybdenum disulfide (MoS<sub>2</sub>) based back-gated field-effect transistors (FETs). Electrical characterization and LFN measurements were conducted on MoS<sub>2</sub> FETs with Al<sub>2</sub>O<sub>3</sub> top-surface passivation. We also studied the effect of top-surface passivation etching on the electrical characteristics of the device. Significant decrease in channel current and transconductance was observed in these devices after the Al<sub>2</sub>O<sub>3</sub> passivation etching. For passivated devices, the two-terminal resistance variation with temperature showed a good fit to the activation energy model, whereas for the etched devices the trend indicated a hopping transport mechanism. A significant increase in the normalized drain current noise power spectral density (PSD) was observed after the etching of the top passivation layer. The observed channel current noise was explained using a standard unified model incorporating carrier number fluctuation and correlated surface mobility fluctuation mechanisms. Detailed analysis of the gate-referred noise voltage PSD indicated the presence of different trapping states in passivated devices when compared to the etched devices. Etched devices showed weak temperature dependence of the channel current noise, whereas passivated devices exhibited near-linear temperature dependence.

Keywords: 2D materials, low-frequency noise,  $MoS_2$ , flicker noise, generation recombination (G-R) noise

S Online supplementary data available from stacks.iop.org/Nano/25/155702/mmedia (Some figures may appear in colour only in the online journal)

### 1. Introduction

Graphene's high carrier mobility and saturation velocity are very attractive features, but the lack of inherent band gap is a challenge for switching applications and low-power electronics [1]. This has led to an exploration of alternative two-dimensional (2D) semiconductor materials. In recent years, molybdenum disulfide (MoS<sub>2</sub>) has attracted significant

<sup>&</sup>lt;sup>1</sup> Department of Electrical and Computer Engineering, George Mason University, Fairfax, VA 22030, USA

<sup>&</sup>lt;sup>2</sup> National Institute of Standards and Technology, Material Measurement Laboratory, Gaithersburg, MD 20899, USA

<sup>&</sup>lt;sup>3</sup> Sensors and Electron Devices Directorate, Army Research Laboratory, Adelphi, MD 20783, USA

<sup>&</sup>lt;sup>4</sup> IREAP, University of Maryland, College Park, MD 20742, USA

Department of Materials Science and NanoEngineering, Rice University, Houston, TX 77005, USA

interest due to the observation of an indirect (1.29 eV) to direct (1.8 eV) band gap transition in monolayer films [2], which opens up exciting possibilities of realizing low-power, high-speed electronic, and optical devices on flexible substrates. MoS2 transistors have exhibited high on-off ratios ( $\sim 10^7$ ), and have shown a subthreshold swing of 74 mV/decade [3]. Combined with high thermal stability and chemical robustness [3, 4], it promises to play an important role in future generation electronics. Few of the recently explored fields include digital electronics [5–7], chemical sensing [8], valley polarization [9, 10], photovoltaics, and photocatalysis [11, 12]. Most of these applications require low distortions in the conduction process and often 1/f noise is the most dominant noise mechanism at low frequencies. Numerous studies have been conducted to understand and reduce 1/f noise in conventional metal-oxide field-effect transistors (MOSFETs) [13-17]. Recently, various groups have also studied 1/f noise in graphene devices [18–20], and lately on MoS<sub>2</sub> FETs [21]. Particularly for MoS<sub>2</sub> devices, there exists a lack of understanding of the dominant mechanisms responsible for the observed current noise. The study of the effect of passivation on LFN in these 2D materials is critical for understanding of the current noise, which is essential for future device applications.

In this paper, we explore the effect of top-surface passivation on the transport and LFN in single-layer MoS<sub>2</sub> FETs. Temperature-dependent (77–300 K) transport and LFN measurements in single-layer MoS<sub>2</sub> back-gated FETs with and after etching Al<sub>2</sub>O<sub>3</sub> passivation are presented. We observed significant nonlinearity and an order of magnitude reduction of channel current after the top passivation layer was etched. Temperature-dependent two-terminal resistance of the passivated devices showed a clear fit to the activation energy model for the entire temperature range (77–300 K), suggesting a band-like transport. For the etched devices two different regimes were identified, indicating a defect-mediated transport. LFN measurements were conducted at various temperatures on both the passivated and etched devices at various back-gate biases. We calculated Hooge parameters in the range of 0.01–0.0001 and 5–0.01 for passivated and etched devices, respectively. The observed gate-dependent noise in both passivated and etched devices could be explained by carrier number fluctuation arising from random trapping and de-trapping of the channel charge carried by the oxide interface traps and correlated surface mobility fluctuation arising from fluctuation of the scattering rates of these traps [22, 23]. Temperature-dependent noise measurement also showed very different behavior for passivated and etched devices.

# 2. Material and methods

Monolayer MoS<sub>2</sub> films were grown directly on a SiO<sub>2</sub>-coated (285 nm) Si substrate using the procedure described in detail by Najmaei *et al* [24]. In brief, high aspect-ratio MoO<sub>3</sub> nanoribbons were used as precursor along with sublimated sulfur in a chemical vapor deposition chamber. The growth process resulted in single crystal MoS<sub>2</sub> triangles with a side length of  $(13 \pm 2.5)~\mu m$ . Electron-beam lithography (EBL)

was used to fabricate variable channel length FETs directly onto the single-layer material avoiding grain boundaries and other defects. The MoS<sub>2</sub> layer was patterned using a CH<sub>4</sub>/O<sub>2</sub> plasma etch, and source and drain contacts were formed by depositing Ti/Au (15 nm/85 nm) using an electron-beam evaporator. A 20 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric was deposited over the samples using atomic layer deposition (ALD), with O<sub>2</sub> plasma and tetramethyl aluminum (TMA) precursors. For the measurements on unpassivated devices, Al<sub>2</sub>O<sub>3</sub> was selectively etched by placing it in MIF300 developer (tetramethylammonium hydroxide based metal–ion free developer) for 30 min at room temperature, followed by a de-ionized water/acetone/isopropanol rinse. Additional details about the processing steps can be found in [25].

The temperature-dependent parametric measurements were performed in an open-cycle cryogenic probe station from Lakeshore using an Agilent B1500A semiconductor parameter analyzer (disclaimer in the notes section). LFN measurements were performed using a cross-correlation technique to minimize the effect of instrument noise [26]. The source-drain bias was provided by the internal batteries of the two independent SRS 570 amplifiers and the gate bias was provided using an independent battery source. A double channel dynamic spectrum analyzer HP 35670A was used in cross-spectrum mode to measure the PSD of the channel current. The LFN measurements were conducted between 1 and 1000 Hz, with frequency resolution of 0.25 Hz and the data was averaged over 20 sets of readings. The temperature-dependent LFN measurements were performed from 77 to 300 K, starting from the lowest temperature.

### 3. Results and discussion

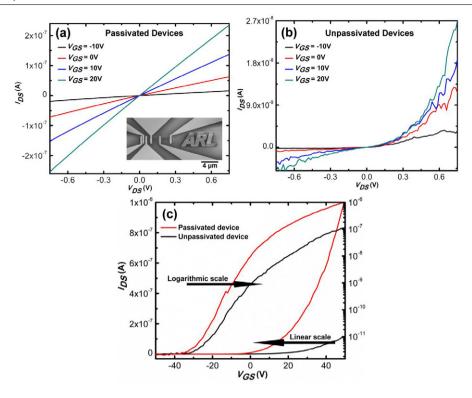

Figures 1(a) and (b) show the drain–source current  $(I_{DS})$  versus drain-source voltage  $(V_{DS})$  characteristics of a MoS<sub>2</sub> transistor at 300 K with gate length (L) and width (W) of 400 nm and 1000 nm, respectively, before and after etching of the top Al<sub>2</sub>O<sub>3</sub> passivation layer. Measurements were performed on both passivated and etched devices in vacuum with chamber pressure in the range of  $10^{-3}$  Pa. The inset of figure 1(a) shows a scanning electron microscope (SEM) image of a typical device. Significant reduction of the channel current (almost an order of magnitude) and non-linearity in the current-voltage characteristics were observed for devices after the passivation was removed (figure 1(b)). A transfer characteristics plot ( $I_{DS}$ versus  $V_{\rm GS}$  at  $V_{\rm DS}=0.5~{\rm V}$ ) is shown in figure 1(c) for the same device with passivation and after passivation has been removed. Clear depletion-mode *n*-channel behavior can be seen in these devices, which is in good agreement with what has been also observed by other groups [2, 3, 27]. The field-effect mobility ( $\mu_{FE}$ ) for these devices was calculated using the following equation:

$$\mu_{\rm FE} = \frac{\partial I_{\rm DS}}{\partial V_{\rm GS}} \frac{L}{W C_{\rm OX} V_{\rm DS}},\tag{1}$$

where  $C_{\rm OX}$  is the gate capacitance per unit area, L is the channel length, W is the channel width,  $V_{\rm DS}$  is the source–drain voltage, and  $\partial I_{\rm DS}/\partial V_{\rm GS}$  is the slope of the

Figure 1.  $I_{DS}-V_{DS}$  plot at 300 K for MoS<sub>2</sub> FET (a) before and (b) after etching of the top passivation. All the I-V curves were taken at constant drain–source voltage ( $V_{DS}=0.5$  V). The inset in (a) shows an SEM micrograph of a typical device. (c)  $I_{DS}-V_{GS}$  plot of the passivated and unpassivated devices plotted in both linear and logarithmic–linear scales at 300 K.

$I_{\rm DS}-V_{\rm GS}$  characteristics taken in the linear region. At 300 K the measured field-effect mobility values were (35.5  $\pm$  2.5) cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and (12.1  $\pm$  1.9) cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for passivated and etched FETs, respectively. All mobility values were measured using four-probe measurement techniques on Hall bar devices at a  $I_{\rm DS}$  of 500 fA, to reduce the contribution of the contact resistances.

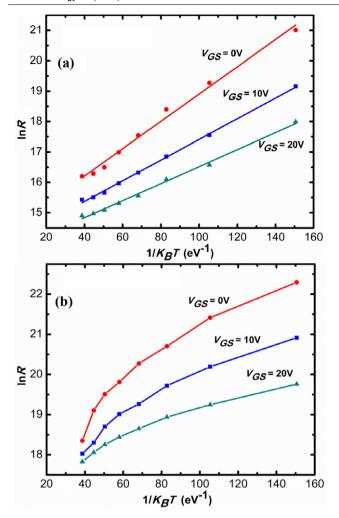

The two-terminal channel resistance for these MoS<sub>2</sub> FETs as a function of measurement temperature is shown for both passivated and etched samples in figure 2. The passivated devices exhibited a good fit to the activation energy model at different gate biases over the entire measurement temperature range, i.e., 77–300 K, as is evident in figure 2(a). This indicates a transport mechanism involving well-defined bands. Using the relationship [22]

$$ln(R) = ln(R_0) + E_a/2k_BT,$$

(2)

where  $R_0$  is the intercept,  $E_a$  is the thermal activation energy of the dopant,  $k_B$  is the Boltzmann constant and T is the absolute temperature, we can calculate the activation energy for conduction in these devices. From the slopes of different curves at different back-gate biases it is clear that the activation energy decreases with increasing back-gate bias (figure 2(a)). On the other hand, etched devices showed two different regimes of conduction for the entire investigated temperature range, with higher activation energy between 200 and 300 K, and weaker temperature dependence between 77 and 200 K, for all three back-gate biases (figure 2(b)). The calculated

activation energies at 20 V back-gate bias were ≈56 meV for passivated devices and ≈32 meV (in the 200-300 K temperature range) for etched devices. In a recent report, Radisavljevic and Kis measured the temperature dependence of the conductance in monolayer MoS<sub>2</sub> back-gated FETs (unpassivated) as a function of back-gate bias [28]. Although a thermally-activated transport model was used to explain the trend, the fit was evident only for temperatures between 166 and 250 K, below which the conductance showed very weak temperature dependence. Surprisingly, the activation energy (computed from their data) is in the range of 20-60 meV for back-gate biases ranging from 2 to 40 V. A very similar trend was also observed by Ayari et al for two-probe conductance variation with temperature for unpassivated MoS<sub>2</sub> monolayers [29]. The calculated activation energy for their result is close to 50 meV for 9 V back-gate bias. The close agreement of the activation energy values for conduction obtained in MoS2 samples fabricated by different methods might indicate the presence of a native defect, which manifests itself as a shallow donor in monolayer materials. Very recently, Qiu et al, reported a very similar trend for temperature-dependent conduction in single-layer MoS<sub>2</sub> FETs and successfully explained the observed trend using hopping conduction through defect-induced localized states [30]—they concluded that the responsible defects were sulfur vacancies. Comparing our results on passivated devices, it is clear that the top-surface passivation renders these surface defects inactive and could be partially responsible

**Figure 2.** Arrhenius plot of the drain–source resistance of the passivated and unpassivated (after etching of the top passivation) FETs at three different gate biases is shown in (a) and (b), respectively. Temperature is in the range of 77–300 K. All the readings were taken at a constant drain–source voltage  $(V_{DS} = 0.5 \text{ V})$ .

for the improved electrical characteristics observed for  $MoS_2$  devices. Raman spectroscopy measurements (see supplemental section available at stacks.iop.org/Nano/25/155 702/mmedia) on etched devices did not indicate any significant structural damage to the  $MoS_2$  layer due to passivation etch.

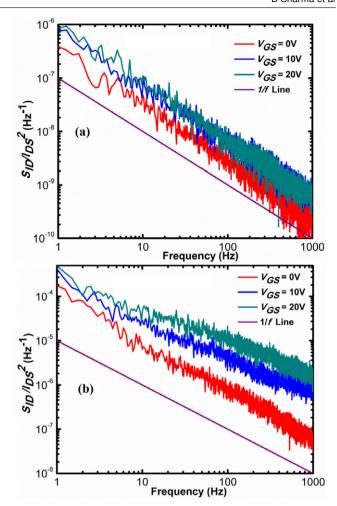

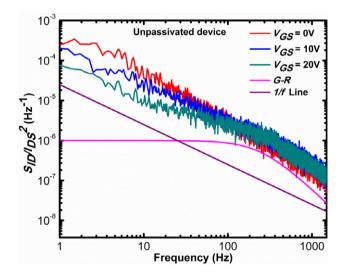

The normalized drain current PSD (=  $S_{\rm ID}/I_{\rm DS}^2$ ) for both passivated and etched devices measured at 300 K at three different gate biases is shown in figures 3(a) and (b). An increase of almost two orders of magnitude in the normalized drain current PSD was observed after the etching of the passivation layer. When  $V_{\rm DS}$  was varied from 0.2 to 2 V, the normalized PSD did not change, indicating that the measured noise is originating from the channel, with minimal contribution from the contacts. The  $S_{\rm ID}/I_{\rm DS}^2$  at 10 Hz were in the range of  $(1-10)\times 10^{-8}$  Hz<sup>-1</sup> and  $(1-10)\times 10^{-5}$  Hz<sup>-1</sup> for passivated and etched devices, respectively. In the case of graphene devices, several groups have reported  $S_{\rm ID}/I_{\rm DS}^2$  in the range of  $10^{-9}$  Hz<sup>-1</sup> to  $10^{-7}$  Hz<sup>-1</sup> at 10 Hz [19, 20, 31].

Irrespective of the mechanisms responsible for the noise, for a device exhibiting 1/f-type noise, the measured PSD can

**Figure 3.** Room temperature (T=300 K) normalized PSD of the drain current for (a) passivated and (b) unpassivated (after etching of the top passivation) devices at different  $V_{\text{GS}}$ . A 1/f trend line is shown for comparison. All the readings were taken at a constant drain–source voltage ( $V_{\text{DS}}=0.5 \text{ V}$ ).

always be described using Hooge's empirical relationship:

$$S_{\rm ID}/I_{\rm DS}^2 = \alpha_{\rm H}/Nf^{\beta},\tag{3}$$

where  $\alpha_{\rm H}$  is the Hooge constant,  $\beta$  (exponential factor) is ideally 1 and N is the total number of carriers approximated as  $N = (V_{\rm GS} - V_{\rm T}) \times L \times W \times C_{\rm OX}/q$  where q is the charge of an electron,  $V_{\rm GS}$  is gate to source voltage, and  $V_{\rm T}$  is the estimated threshold voltage. Although for 2D materials, the validity of the model is questionable, it provides a figure of merit, i.e., Hooge constant, which allows for direct comparison of the noise levels in various devices. In our case the calculated variation in  $\beta$  is  $1 \pm 0.2$  for etched devices and  $1 \pm 0.09$  for passivated devices. The calculated Hooge parameter ranges are between (0.01 and 0.0001) and (5 and 0.01) for passivated and etched devices, respectively. Recently, a Hooge parameter ranging between 0.005 and 2 has been reported for unpassivated MoS<sub>2</sub> FETs [21].

We have used the 'unified model' which takes into account both carrier number fluctuation along with correlated mobility fluctuation to explain the observed LFN trends in these devices. Carrier number fluctuations arise from dynamic trapping and de-trapping of free carriers by oxide–semiconductor interface traps. In addition, trap charge fluctuations may result in scattering rate fluctuations, which causes fluctuation of the inversion layer mobility. It is worth pointing out that the Hooge mobility fluctuation is a bulk effect, whereas the correlated mobility fluctuation is a surface effect resulting from carrier number fluctuation through interface traps. In analyzing the noise, we have used the framework proposed by Ghibaudo  $et\ al$ , where normalized drain current spectral density  $(S_{\rm ID}/I_{\rm D}^2)$  and input-referred gate-voltage spectral density  $(S_{\rm VG})$  are given by the following relationships [22, 23]:

$$\frac{S_{\rm ID}}{I_{\rm D}^2} = \left(1 + \alpha \mu_{\rm eff} C_{\rm OX} \frac{I_{\rm D}}{g_{\rm m}}\right)^2 \left(\frac{g_{\rm m}}{I_{\rm D}}\right)^2 (S_{\rm VFB}) \tag{4}$$

$$S_{VG} = S_{VFB} \left[ 1 + \alpha \mu_{eff} C_{OX} (V_{GS} - V_T) \right]^2,$$

(5)

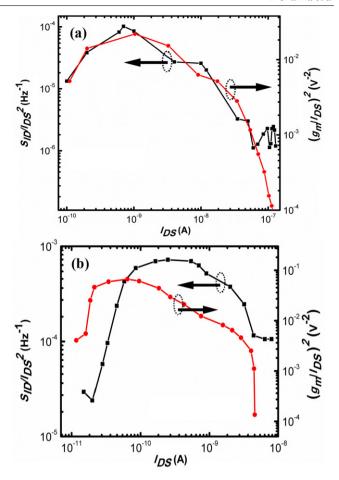

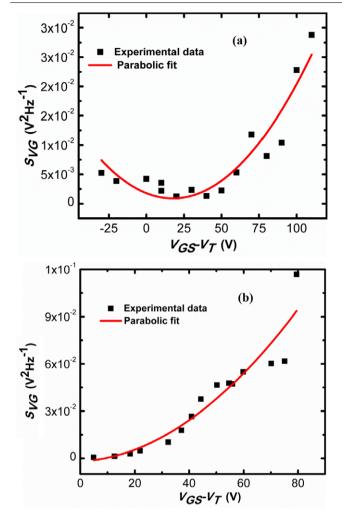

where  $\alpha$  is the Coulomb scattering coefficient ( $\approx 10^4$  V s C<sup>-1</sup> for electrons and  $\approx 10^5$  V s C<sup>-1</sup> for holes),  $\mu_{\rm eff}$  is the low-field effective mobility,  $C_{\text{OX}}$  is the gate capacitance,  $V_{\text{T}}$  is the threshold voltage and SVFB is the flat-band voltage spectral density. The S<sub>VFB</sub> is related to interface charge spectral density per unit area  $(S_{\text{Oit}})$  as  $S_{\text{VFB}} = S_{\text{Oit}}/(WLC_{\text{OX}}^2)$ . It should be mentioned that equations (4) and (5) are generally valid for inversion-mode MOSFETs [22, 23]. Although MoS<sub>2</sub> FETs presented in this study are n-channel depletion-mode devices, the close proximity of the channel charge carriers to the interface can lead to similar fluctuation mechanisms as in inversion-mode FETs. In our case, all measurements were performed in the linear region of operation. The dominant mechanism can be highlighted by plotting the normalized drain current spectral density as a function of drain current  $(I_{DS})$  in a log-log scale. In the case of Hooge's mobility fluctuation, i.e., bulk mobility fluctuation, the normalized drain-current PSD should be proportional to  $1/I_{DS}$ . If the normalized drain-current PSD varies with the drain current as  $(g_{\rm m}/I_{\rm DS})^2$ , i.e.,  $S_{\rm ID}/I_{\rm DS}^2 \propto (g_{\rm m}/I_{\rm DS})^2$ , then it is likely that the carrier number fluctuation is the dominant source of the 1/f noise. Moreover, if the associated gate-referred voltage PSD (S<sub>VG</sub>) exhibits parabolic gate-voltage dependence, then correlated mobility fluctuation is also present. Figures 4(a) and (b) present  $S_{\rm I}/I_{\rm DS}{}^2$  as a function of drain current in a log-log plot. It is worth pointing out that significant variation in  $S_{\rm I}/I_{\rm DS}^2$  as a function of  $I_{\rm DS}$  is observed by varying  $V_{\rm GS}$ in a wide range of values. As is evident from figure 4(a) the passivated device demonstrates a near-ideal fit. The deviation at higher drain currents is due to the excess noise from the source/drain contact resistances [22]. For etched devices (figure 4(b)) the agreement is not exact. Figures 5(a) and (b) present gate-referred voltage PSD (SvG) as a function of  $(V_{GS}-V_T)$ . For both passivated and etched devices the parabolic dependence is evident, indicating that correlated mobility fluctuation is also present. In the absence of correlated mobility fluctuation, the gate-referred noise voltage will be constant as a function of gate bias. For passivated devices, a minimum in the plot of gate-referred voltage PSD as a function of  $(V_{GS}-V_T)$  is observed. Interestingly, Ghibaudo

**Figure 4.** Comparison of normalized PSD of the drain current at  $f=1~{\rm Hz}$  and  $(g_{\rm m}/I_{\rm DS})^2$  at different  $I_{\rm DS}$  for passivated and unpassivated (after etching of the top passivation) devices in (a) and (b), respectively. All the readings were taken at a constant drain–source voltage  $(V_{\rm DS}=0.5~{\rm V})$ .

et al demonstrated that by mixing acceptor- and donor-like traps in the noise model, one can generate a minimum in the parabolic plot of gate-referred voltage PSD, whereas a pure acceptor-like trap has no minimum, as seen in the case of the etched devices [23].

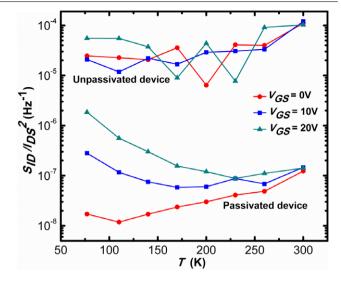

Figure 6 presents temperature-dependent  $S_{\rm I}/I_{\rm DS}^2$  at 10 Hz for both etched and passivated devices at three different gate biases. The drain current noise in the etched device shows very weak temperature dependence at all three gate biases. This could indicate that the physical trapping mechanism responsible for 1/f noise is dominated by a tunneling process. In contrast, the nearly linear normalized drain current spectral density at 0 V gate bias indicates a more thermally-activated trapping process [22, 23]. However, the reason behind the increase in noise due to positive gate bias in the case of passivated devices is not clear. It is also interesting to note that the temperature-dependent field-effect mobility measured on passivated and etched devices showed very similar trends, i.e., the measured field-effect mobility had linear dependence with temperature for the passivated devices, whereas for the etched devices the mobility showed very weak temperature dependence [25]. We can speculate that the nature of transport

**Figure 5.** The experimental input gate-referred PSD voltage obtained at different  $V_{\rm GS}$  values for (a) passivated and (b) unpassivated (after etching of the top passivation) devices. Parabolic fit to the measured data points is also shown. All the readings were taken at a constant drain–source voltage ( $V_{\rm DS}=0.5~\rm V$ ).

is different in passivated and etched devices, which ultimately determines the temperature-dependent characteristics of noise in the single-layer MoS<sub>2</sub> devices.

Etched devices showed the presence of Lorentzian peaks associated with generation-recombination (G-R) noise in addition to 1/f noise. However, for all the etched devices, transition from G-R to 1/f and vice versa was observed during the course of repeated measurements. The PSD associated with G-R noise exhibits a Lorentzian behavior, i.e.,  $S_{\rm ID} =$  $A/(1+(f/f_0)^2)$ , where A is the low-frequency amplitude and  $f_0$  is the characteristic frequency. Figure 7 shows the PSD of an etched device at 170 K exhibiting G-R related Lorentzian shape in addition to the excess 1/f noise. In the case of graphene, few groups have reported G-R noise and this is attributed to defects on the edges of Graphene channels giving rise to a characteristics time constant in the fluctuations of carriers [20]. A recent report by Sangwan et al also showed the presence of G-R peaks at low temperature in unpassivated  $MoS_2$  devices [21]. The single time constant Lorentzian peaks

**Figure 6.** Temperature-dependent (77–300 K) normalized PSD of the drain current noise at f=10 Hz at different temperatures for passivated and unpassivated (after etching of the top passivation) devices. All the readings were taken at constant drain–source voltage ( $V_{\rm DS}=0.5$  V).

**Figure 7.** Normalized PSD of the drain current noise for unpassivated (after etching of the top passivation) devices at T=170 K. The 1/f trend line as well as ideal single time constant Lorentzian-type PSD, i.e.  $S_{\rm I}=A/(1+(f/f_0)^2)$  due to G-R noise are shown for illustration. The green line (PSD at  $V_{\rm GS}=20$  V) clearly indicates the presence of G-R noise in addition to excess 1/f noise. All the readings were taken at constant drain–source voltage ( $V_{\rm DS}=0.5$  V).

in 1/f PSD is due to the presence of discrete traps or G-R centers within the band. For unpassivated devices this could result from the defect sites on the top surface of the  $MoS_2$  film. However, the unstable nature of the G-R peaks observed in unpassivated devices might be associated with adsorption of molecules at surface defect sites. For example, Balandin *et al* clearly showed the evolution of characteristic Lorentzian peaks in 1/f spectra in graphene devices, due to the adsorption of specific molecules [18].

### 4. Conclusion

In summary, we have examined the effects of passivation on transport and LFN in single-layer MoS<sub>2</sub> FETs. Temperaturedependent resistance measurements in single-layer MoS2 FETs passivated with ALD-deposited Al<sub>2</sub>O<sub>3</sub> indicated a band-like transport mechanism, whereas for etched devices weak temperature dependence of the resistance pointed to a defect-mediated transport mechanism. It was clear that top-surface passivation significantly reduces the drain current noise. For both passivated and etched devices, the bias-dependent LFN at 300 K can be explained by carrier number fluctuation and correlated mobility fluctuation; both related to surface effects. Correlation to the bulk mobility fluctuation model (Hooge's model) was not observed. Temperature-dependent noise measurements showed very weak dependence for etched devices compared to passivated devices. In general, the findings presented in this paper should contribute to the much needed advancements in 2D material interface engineering for device applications.

# **Acknowledgments**

This work is partially supported by National Science Foundation under grant no. ECCS-0112802. MA, PBS, AGB and MD acknowledge the support of the US Army Research Laboratory (ARL) Director's Strategic Initiative (DSI) program on interfaces in stacked 2D atomic layered materials. SN and JL would like to acknowledge Welch Foundation grant C-1716 and the NSF grant ECCS-1327093 for their support. SN and PMA would also like to thank the support of the US Army Research Office MURI grant W911NF-11-1-0362. The authors would also like to thank Dr Pani Varanasi, ARO for in-depth technical discussion on 2D atomic layers R&D. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the ARL or the US Government. The US Government is authorized to reproduce or distribute reprints for Government purposes notwithstanding any copyright notation herein.

*Notes.* Certain commercial equipment, instruments, or materials are identified in this paper to foster understanding. Such identification does not imply recommendation or endorsement by the National Institute of Standards and Technology nor does it imply that the materials or equipment identified are necessarily the best available for the purpose.

# References

- [1] Wu Y Q, Lin Y M, Bol A A, Jenkins K A, Xia F N, Farmer D B, Zhu Y and Avouris P 2011 *Nature* 472 74–8

- [2] Mak K F, Lee C, Hone J, Shan J and Heinz T F 2010 Phys. Rev. Lett. 105 136805

- [3] Radisavljevic B, Radenovic A, Brivio J, Giacometti V and Kis A 2011 Nature Nanotechnol. 6 147–50

- [4] Bertolazzi S, Brivio J and Kis A 2011 ACS Nano 5 9703–9

- [5] Radisavljevic B, Whitwick M B and Kis A 2011 ACS Nano 5 9934–8

- [6] Wang H, Yu L L, Lee Y H, Shi Y M, Hsu A, Chin M L, Li L J, Dubey M, Kong J and Palacios T 2012 Nano Lett. 12 4674–80

- [7] Wang H et al 2012 IEEE International Electron Devices Meeting (IEDM)

- [8] Perkins F K, Friedman A L, Cobas E, Campbell P M, Jernigan G G and Jonker B T 2013 Nano Lett. 13 668–73

- [9] Mak K F, He K L, Shan J and Heinz T F 2012 *Nature Nanotechnol.* **7** 494–8

- [10] Xiao D, Liu G B, Feng W X, Xu X D and Yao W 2012 Phys. Rev. Lett. 108 196802

- [11] Gourmelon E, Lignier O, Hadouda H, Couturier G, Bernede J C, Tedd J, Pouzet J and Salardenne J 1997 Sol. Energy Mater. Sol. C 46 115–21

- [12] Zong X, Yan H J, Wu G P, Ma G J, Wen F Y, Wang L and Li C 2008 J. Am. Chem. Soc. 130 7176

- [13] Hung K K, Ko P K, Hu C M and Cheng Y C 1990 *IEEE*Trans. Electron Devices 37 654–65

- [14] Jordan A G and Jordan N A 1965 IEEE Trans. Electron Devices Ed12 148

- [15] Tian H and Gamal A E 2001 *IEEE Trans. Circuits Syst. II:*Analog. Digit. Signal Process. 48 151–7

- [16] Xu J and Deen M J 2002 Electron. Lett. 38 429–31

- [17] Videnovic-Misic M and Jevtic M M 2008 *Microelectron*. *Reliab.* **48** 1008–14

- [18] Balandin A A 2013 Nature Nanotechnol. 8 549-55

- [19] Lin Y M and Avouris P 2008 Nano Lett. 8 2119-25

- [20] Shao Q H, Liu G X, Teweldebrhan D, Balandin A A, Runryantsev S, Shur M S and Yan D 2009 *IEEE Electron*. *Device Lett.* **30** 288–90

- [21] Sangwan V K, Arnold H N, Jariwala D, Marks T J, Lauhon L J and Hersam M C 2013 Nano Lett. 13 4351–5

- [22] Ghibaudo G 2003 Proc. Soc. Photo Opt. Instrum. 5113 16-28

- [23] Ghibaudo G, Roux O, Nguyenduc C, Balestra F and Brini J Phys. Status Solidi. A 124 571–81

- [24] Najmaei S, Liu Z, Zhou W, Zou X L, Shi G, Lei S D, Yakobson B I, Idrobo J C, Ajayan P M and Lou J 2013 Nature Mater. 12 754–9

- [25] Amani M, Chin M L, Birdwell A G, O'Regan T P, Najmaei S, Liu Z, Ajayan P M, Lou J and Dubey M 2013 Appl. Phys. Lett. 102 193107

- [26] Sharma D, Motayed A, Krylyuk S, Li Q L and Davydov A V 2013 IEEE Trans. Electron Devices 60 4206–12

- [27] Fontana M, Deppe T, Boyd A K, Rinzan M, Liu A Y, Paranjape M and Barbara P 2013 Sci. Rep. 3 1634

- [28] Radisavljevic B and Kis A 2013 Nature Mater. 12 815–20

- [29] Ayari A, Cobas E, Ogundadegbe O and Fuhrer M S 2007 J. Appl. Phys. 101 014507

- [30] Qiu H et al 2013 Nature Commun. 4 2642

- [31] Zhang Y, Mendez E E and Du X 2011 ACS Nano 5 8124–30